# International Journal of Advance Research in Engineering, Science & Technology

e-ISSN: 2393-9877, p-ISSN: 2394-2444 Volume 3, Issue 1, January-2016

# Wideband Low Noise Amplifier for Next Generation Wireless RF Frontend: A Review Paper

Hasmukh P Koringa<sup>1</sup>, Dr. Vipul A Shah<sup>2</sup>

<sup>1</sup>Assistant Professor, Government Engineering College Rajkot, Gujarat, India <sup>2</sup>Professor and head of Dept, I&C Department, DDU, Nadiad, Gujarat, India

#### Abstract

The volatile growth of the wireless industry, global access to the internet, and the ever increasing demand for high speed data communication are encourage us toward rapid developments in communication technology. Wireless communication plays an essential role in this transformation to the next generation of communication systems. Next generation wireless terminal should support multiple communication standards with different modulation scheme require wideband Radio Frequency (RF) frontend having high gain, low noise figure (NF), good linearity and low power consumption. This can be done using software define radio (SDR) architecture. In SDR architecture of receiver Low Noise Amplifier (LNA) is essential part. In this paper we done meticulous survey of wideband LNA topologies published in open literature suitable for SDR. Measured results of the sample LNA designs from each category are tabulated and discussed with emphasis on gain, NF, input matching, power consumption, and linearity tradeoffs. At the end discuss design challenges of next generation RF frontend wideband LNA.

Keywords- LNA; Next Generation Wireless Receiver; RF Frontend; SDR; Wideband;

#### I. Introduction

Today's wireless mobile terminal should support multiple communication standards like: GSM, UMTS, WiMAX, LTE, ZigBee, Bluetooth, IEEE 802.11a/b/g etc; operated on difference frequency band and different modulation scheme [1]. This mobile terminal is termed as commercial Software Defined Radio(SDR), as proposed by Mitiola [2].

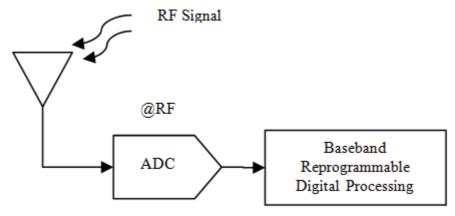

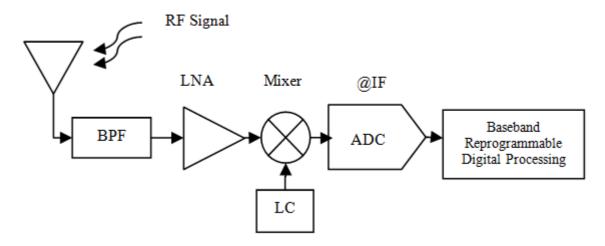

The ideal SDR architecture proposed by Mitiola (Figure 1) puts very tough requirements on the dynamic range, speed, noise performance and linearity of A/D converter. A practical SDR architecture as shown in figure 2. An LNA relaxes the noise performance and dynamic range requirements while the mixer block reduces the speed requirements of the A/D converter by converting RF signal to IF signal. That is why Low Noise amplifier is essential part in wideband RF Frontend design.

Moreover, the user expectations are major drivers to determine upper bound on power consumption and cost metrics. The new portable wireless products cannot be sold in the market if their battery backup time is shorter. The same principle rules the cost and budgeting paradigm. Thus, future LNAs should have power consumption, gain and NF close to what is offered by state-of-the- art narrowband LNA designs. The bandwidth should be more than 6 GHz to cover all the deployed commercial and upcoming 4G standards.

Figure 1. Ideal SDR Receiver.

Figure 2. Practical SDR receiver.

#### II. CHALLENGES IN WIDEBAND LNA DESIGN

In [8], the gain, NF and linearity requirements of a single LNA accommodating GSM, UMTS and WLAN are specified as 23dB, 3 dB and 0dBm respectively. Addition of new standards like WiMAX and LTE will make the LNA specifications even more challenging. Moreover, multiple filters are used at the LNA input to remove blockers.

The linearity parameters of the LNA will become more stringent if these filter specifications are relaxed. This clearly shows that the implementation of a receiver chain without an LNA is practically impossible. In a receiver, the first amplifying block is LNA. Its noise performance defines the NF of complete receiver. A classical narrowband LNA should have high gain, low NF, good linearity, low power, 50  $\Omega$  matching and stability at the frequency of interest. To accommodate different standards with different modulation scheme require specification of wideband LNA are:

- Minimum signal reflection by achieving good (50  $\Omega$ ) input matching (S11 $\leq$ -15dB)for all frequencies [6].

- NF $\leq$ 3.5 dB over the entire bandwidth [7].

- Higher linearity (IIP3≥0 dBm) [8].

- Flat gain across the entire bandwidth.

- Unconditional stability over entire frequency range.

#### III. WIDEBAND LNA TOPOLOGIES

The major challenges of a wideband LNA design can be summarized in terms of S parameters and NF as follows: [24] you.

- Forward gain degradation (decreases in S21) which necessitates some techniques to compensate the gain roll-off.

- Frequency variations of S11 and S22.

- Increase in |S12| which will reduce the forward gain and increase the possibility of oscillation and instability.

- NF degradation at high frequencies.

To address these challenges in the design of a wideband LNA, several topologies and circuit techniques have been proposed in the literature. In This section, we will introduce briefly some of the popular wideband architectures and briefly discuss their advantages and disadvantages.

#### A. Common source with resistive termination:

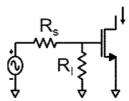

One good approach to achieve wideband impedance matching is by adding a  $50\Omega$  shunt resistor at the input of common source LNA as shown in Figure 3[3]. This topology results in severe tradeoff between NF optimization and input impedance matching. The placement of shunt resistor before the transistor not only attenuates the signal but also add thermal noise. The minimum NF of this approach is [3].

International Journal of Advance Research in Engineering, Science & Technology (IJAREST) Volume 3, Issue 1, January 2016, e-ISSN: 2393-9877, print-ISSN: 2394-2444

$$NF = 1 + \frac{R_s}{R_I} + \frac{\gamma R_s}{g_m} \left( \frac{1}{R_s} + \frac{1}{R_I} \right)^2 + \gamma g_m R_s \frac{\omega^2}{\omega_T^2}$$

(1)

where  $\gamma$  is a noise parameter and  $\alpha$  is the ratio of transistor's transconductance (gm) to drain-source conductance (gds) at zero bias.  $\omega_T$  is the unity gain crossover frequency.

Figure 3. Common source with resistive termination.

#### B. Comman Gate

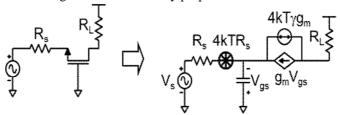

In common gate input impedance is 1/gm which is inversely propos anal to transconductance of device. To match

Figure 4. Common gate and its small signal euivalent circuit.

Input admittance Yin=gm+sCgs at lower frequency inout impedance Zin=1/gm. Noise performance of CG structure can be calculated as

$$G_{eff} = \frac{I_{out}}{V_s}$$

$$= \frac{-g_m}{1 + g_m R_s + s R_s C_{gs}}$$

$$G = \left| G_{eff} \right|^2 = \frac{g_m^2}{(1 + g_m R_s)^2 + \omega^2 (R_s C_{gs})^2}$$

$$NF = \frac{N_{device} + G \cdot N_{in}}{G \cdot N_{in}} = 1 + \frac{4kT\gamma g_m}{4kTR_s \frac{g_m^2}{(1 + g_m R_s)^2 + \omega^2 (R_s C_{gs})^2}}$$

$$= 1 + \frac{\gamma}{R_s g_m} \left[ (1 + g_m R_s)^2 + \omega^2 R_s^2 C_{gs}^2 \right]$$

$$= 1 + 4\gamma + \gamma \frac{\omega^2}{\sigma^2}$$

$$= 1 + 4\gamma + \gamma \frac{\omega^2}{\sigma^2}$$

$$(2)$$

$=1+4\gamma+\gamma\frac{\omega^2}{\omega_T^2}$ Power Transfer of CG Structure

$R_s = R_L = R = 50 \text{ ohm}$

$$S_{11} = \frac{Z_{in} - Z_s^*}{Z_{in} + Z_s} = \frac{1 - g_m R_s - s R_s C_{gs}}{1 + g_m R_s + s R_s C_{gs}}$$

$$= \frac{-s R_s C_{gs}}{2 + s R_s C_{gs}}$$

$$S_{21} = 2R_L G_{eff} = \frac{2R_L g_m}{1 + g_m R_s + s R_s C_{gs}}$$

$$= \frac{2}{2 + s C}$$

(6)

$S_{11}=0$ ,  $S_{21}=1$  @ Low frequency

NF is low due to no extra resistive noise source as well as NF is independent of power consumption.

In [40] used Common Gate with current reuse Common Source next stage to enhance gain and achieved good gain 14.9dB at power consumption is only 3.4mW in 2.4-11.2GHz band.

#### C. Negative Feedback Wideband LNA

The classical approach to satisfy the required impedance matching at the input of a wideband LNA is to employ negative feedback. This technique will provide a flat gain and reduces the sensitivity of the circuit to the MOS device parameters. The feedback circuitry may increase the minimum *NF* and reduce the maximum achievable gain.

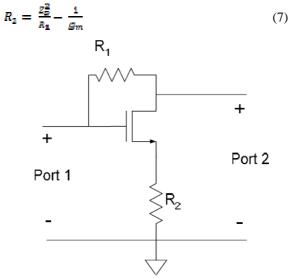

Different topologies of negative feedback amplifier exist in the literature. One of the most popular variations of negative amplifier is the shunt-series amplifier, symbolically shown in figure 5.

To achieve wideband input and output matching, one should design for zero s11 and s22 after finding the S parameter expressions for this network. Solving for s11=s22=0, yields the following equation that relates the values of R1 and R2 [9]:

Figure 5. Two port model of a shunt-series amplifier [48]

An appropriate choice of R1 and R2 values will satisfy (7) and hence the input and output matching. It will also result in a flat in-band forward gain with no dependency on the MOS device parameters ([9]). However, (7) is only valid in low frequencies where all parasitic effects may be ignored. In gigahertz applications parasitic capacitances and inductances become non-negligible and the power gain starts to roll-off. The input and output matching also degrades significantly in high frequencies.

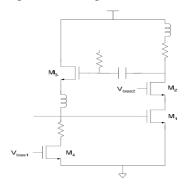

One implementation of a negative feedback amplifier is shown in figure 6. In this circuit [10] the input stage is a common source amplifier and the feedback stage is a common drain amplifier. A simple analysis of this circuit shows that  $gm_1M_2$  of the common drain stage controls the input impedance, while  $gm_1M_1$  of the common source amplifier contributes to the gain and NF of the overall LNA. This is in contrast to the 1/gm termination architecture where the gm of the input transistor is set by the input matching requirements and leaves no freedom for NF optimization. The main disadvantage of this architecture is the relatively high power consumption due to the addition of the feedback stage.

In another work, negative feedback is employed to realize a UWB LNA covering a 7GHz bandwidth (2-9 GHz) [11]. The schematic of this LNA is shown in figure 7. The input stage adopts a shunt-series feedback structure to satisfy the wideband input matching. The inverter configuration at the input is to increase the total trans-conductance (gm1+gm2), and hence the open-loop voltage gain for a fixed power consumption.

Figure 6. Common drain feedback LNA [48]

The increase in the total transconductance also allows for a higher shunt resistor for a given 3dB bandwidth. This increase in the value of shunt resistance will lend itself to a lower total NF. Two degeneration inductances Ls1 and Ls2 are used to partially cancel the parasitic capacitances at the input of the LNA, which would otherwise devastate the impedance matching at high frequencies. The second stage is a simple cascode amplifier with a shunt-peaking load that provides the required gain of the entire LNA [48].

Figure 7. Two-stage LNA for UWB applications [48]

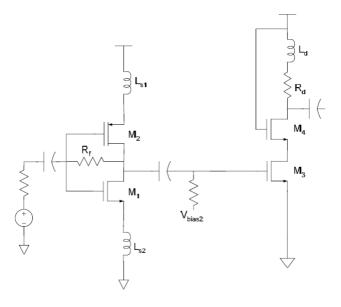

Negative feedback amplifiers may also be used as the second stage of wideband amplifiers. One example is the work in [12] that combines the benefits of 1/gm termination with those of the negative feedback amplifier. Figure 8 depicts the schematic of this architecture. The input stage uses a common-gate amplifier to achieve  $50\Omega$  impedance matching. However, this matching sets the value of gm,M<sub>1</sub>, and another stage is required to provide sufficient gain over the entire band-width. This second stage is realized by employing M<sub>2</sub> in a shunt-feedback configuration. One drawback of this feedback is that the degradation of forward gain at high frequencies causes a positive feedback through Rf., thus leading to oscillation at the output. To alleviate this problem, L<sub>f</sub> is connected in series with the shunt resistor, Rf. This will reduce the feedback at high frequencies and also improve the gain flatness. L<sub>d1</sub> and L<sub>d2</sub> are inductive loads to compensate the gain degradation at high frequencies[48].

Figure 8. Two stage wideband LNA for UWB applications [48]

In [12], a UWB LNA is successfully designed and simulated using this two-stage architecture.

The Common Gate (CG) LNA is good solution of wideband input matching. Also, CG LNA have good linearity, stability and low power consumption. However its main drawback is the relatively high NF and low gain due to input impendence matching need to restrict value of trans-conductance. Different negative feedback techniques are used in CG LNA like capacitive cross coupling, dual negative feedback, and positive –negative feedback to overcome tradeoff between input impendence matching and the NF, which lead to simultaneous reduction in noise and power dissipation. In

[39] authors have proposed inductorless multiple feedback paths CG LNA and achieve 1.85dB minimum NF, 23dB Gain with good linearity (IIP3=-2.3dBm) at a low power dissipation (2.8mW) in 0.1-1.77GHz band. In [41] proposed pseudo-differential resistive feedback wideband LNA with noise and distortion cancellation.

In [42] proposed linearization techniques for wideband LNA by using inverter topology with resistive feedback in first stage to provide high linearity and cascode amplifier with shunt series inductive peaking to extend bandwidth and achieve high gain simultaneously in second stage. The proposed [42] wideband LNA achieve good linearity +6.4dBm IIP3, 15dB gain, 3.5dB minimum noise figure and 16.2mW power consumption in entire 3.1 -10.6GHz band.

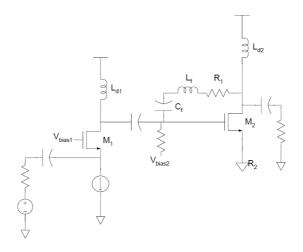

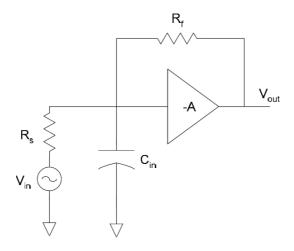

The aforementioned trade-offs among power, bandwidth, and gain are a serious drawback of any feedback system. For illustration purposes, consider the conceptual schematic of a shunt feedback amplifier as shown in figure 9. The input impedance is given by Zin(s)=Rs/(1+sRsCin), where Rf and A are chosen in a way that Rf/(1+A)=Rs. In order to achieve input matching at 10GHz, i.e.,  $|\Gamma| < -10$ dB, the input capacitance (Cin) is limited to as low as 200fF [13]. This limits the width of the input transistor and hence the maximum gain of this stage. To overcome this problem, most of the feedback amplifiers must include a second stage to boost the gain. Two stages of gain directly translate into higher power consumption, which is not a desirable outcome[48].

Figure 9. Simplified block diagram of a shunt-feedback LNA [48]

#### D. Thermal-noise-cancelled Wideband LNA

Feedback amplifiers, as discussed earlier, typically require two stages of amplification in order to provide sufficient gain and thus dissipate a large amount of power. Also note that the input impedance in a feedback amplifier is a function of the amplifier gain. However, this dependency is not straightforward, and the impedance matching is susceptible to the variations of the gain.

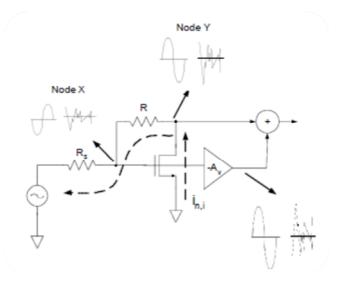

To overcome these shortcomings, [14] suggests the use of a noise-cancelling feed-forward technique that decouples noise and input matching requirements. The conceptual schematic of this LNA is shown in figure 10. The noise current of the amplifier, In,i flows out of the MOS device and passes through R and Rs. Therefore, the instant noise voltages at nodes X and Y have the same polarity. Conversely, the signals at X and Y are of opposite polarities, simply due to the negative gain of the amplifier. This difference between the sign of signal and noise suggest the possibility of cancelling the noise while boosting the signal up.

To do so, another gain stage is inserted between the first stage and the output. The voltage at node Y (signal plus noise) is added with the properly scaled negative replica of the voltage at node X (the block shown by -Av generate this replica)[15]. By the proper choice of Av, the noise contribution of the MOS device becomes equal to zero, and a low NF can be obtained over a wide range of frequency. The analysis in [15] derives the appropriate value of Av in terms of circuit elements R and Rs:

$$A_v = 1 + \frac{R}{R_v} \tag{8}$$

It is also shown that, under these conditions, the noise contribution of different components is as follows:

Figure 10. Schematic of thermal noise cancelling technique [48]

The idea of noise cancellation can be extended to any type of amplifier that has 1) a stage of impedance matching, 2) an auxiliary amplifier for sensing the voltage across a real input source, and 3) a circuit to combine the output of two amplifiers to cancel out the noise of the impedance matching stage. Some implementations of this idea are proposed in the same paper[48].

Despite all these benefits, the dominant pole at the input (node X) may limit the bandwidth at high frequencies. Furthermore, due to the existence of the parasitic capacitances, *NF* increases quadratically with the frequency. These effects, along with the high power consumption required by the two amplifiers, may limit the applications of this architecture.

Wideband noise cancelling LNAs reported in literature consume very large power because of the addition stages require for noise cancelling. This make them inappropriate for portable applications. In [46] authors have proposed novel current reuse LNA with noise cancelling technique. And achieve 9.97mW power consumption with gain 10.3dB, NF 3.68dB in entire 2.35-9.37GHz band.

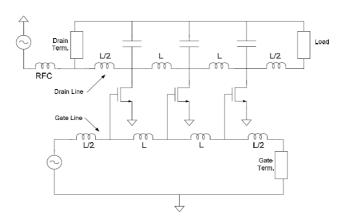

Figure 11. Schematic of a basic distributed amplifier [48]

### E. Distributed Amplifier

Distributed amplifiers (DA) (also known as travelling wave amplifiers) employ an architecture in which several active devices are connected in parallel [17]. A basic distributed amplifier is shown in figure 11. The output current of individual amplifiers combine in an additive fashion, and this dictates a relatively low gain for this architecture. The advantage of this architecture comes from the fact that the input capacitances of these amplifiers are distributed in an LC network which allows for the realization of amplifiers with large bandwidths. In fact, the series inductive elements and capacitances of MOS devices form an artificial transmission line, which allows the flow of the signal to the end of the gate line. The signal fed to the gate of the MOS device is transferred to the drain line through the trans-conductance (gm) of the device. If the phase velocity on the gate and drain lines are identical, then the signals at the output add in the forward direction as they arrive at the output. Many wideband LNAs in CMOS have been realized using DA architectures [18][19]. However, the large power consumption of this architecture is a major drawback and makes it unsuitable for low-power portable systems.

These architectures are the most well-known works in the literature of wideband LNA design. Although successfully implemented for some applications, there are still many issues that need to be addressed when it comes to the design of highly integrated LNAs. For instance, the large power consumption of most of these architectures is a major problem, which may eliminate the feasibility of their integration for low-power multi-standard applications. Moreover, a well established methodology is needed to provide the general guidelines for the design of wideband and multi-standard LNAs [48].

#### IV. CONCLUSION

In this paper, we have presented a rigorous study of different types wideband LNAs published in open literature. Most of all published topologies of wideband LNA used CMOS technology of choice for future commercial RFICs due to its supreme integration capability and extremely low cost per transistor. Here comparison of wideband LNAs done based on its circuit topologies used instead of the technology node used for manufacturing. The main purpose of this review is to find potential circuit topologies suitable for future wireless RF Frontend wideband LNAs. The LNAs are one of the major hurdles and their successful realization will pave the way to commercial SDR.

A simple link budget spreadsheet of today's majority standards shows that linearity is the most exigent requirement as posed by the legacy of GSM standard (0dBmblocker). Therefore, P1dB of higher than 0dBm has proved to be the toughest requirement on multi-standard LNAs. None of the LNAs reported so far meet the requirements of NF, gain, impedance matching, power consumption and linearity simultaneously. There are several reported designs which come close to achieving these specifications except for linearity (P1dB, IIP2, and IIP3) requirements. If we take a closer look, we realize that the linearity requirements (P1dB 0 dBm) along with gain 10dB cannot be met in50  $\Omega$  impedance matched circuits implemented in nanometer CMOS. This linearity-gain tradeoff becomes more stringent as the power supply scales down in latest technology nodes. As the P1dB or IIP3 cannot exceed supply voltage, hence better linearity with recent nodes is a major limitation in existing LNA designs.

| TABLE I. LITERATURE SURVET OF WIDEBAND LOW NOISE AMPLIFIER |                            |             |          |         |               |                              |                                                   |

|------------------------------------------------------------|----------------------------|-------------|----------|---------|---------------|------------------------------|---------------------------------------------------|

| Source                                                     | CMOS<br>Technology<br>(um) | BW<br>(GHz) | S21 (dB) | NF (dB) | IIP3<br>(dBm) | Power<br>Consumption<br>(mW) | Topology                                          |

| JSSC-2004 [20]                                             | 0.25                       | 0.002-1.6   | 13.7     | 2.4     | 0             | 35                           | R FB +NMOS/PMOS                                   |

| JSSC-2004 [21]                                             | 0.18                       | 2.3-9.2     | 9.3      | 4       | -6.7          | 9                            | CS + degeneration and input BPF                   |

| JSSC-2005 [22]                                             | 0.18                       | 2-4.6       | 9.8      | 2.3     | -7            | 12.6                         | CS + series RC FB                                 |

| ICAT-2005 [23]                                             | 0.18                       | 2.7-9.3     | 10       | 3.3     | -0.3          | 14                           | Cascode + input HPF                               |

| JSSE-2006 [24]                                             | 0.18                       | 3.1-10.6    | 9.5      | 5-5.6   | -13           | 9.4                          | Cascode + input filter                            |

| JSSCC-2006 [25]                                            | 0.18                       | 3-5         | <16      | 2.2     | -9            | 7.68                         | CS + miller effect input matching filter          |

| JSSC-2006 [26]                                             | 0.18                       | 0.04-7      | 8.6      | 4.2     | +3            | 9                            | Distributed cascode                               |

| JSSC-2007 [27]                                             | 0.13                       | 3.1-10.6    | 15.1     | 2.5     | -8.5          | 9                            | CS + reactive FB                                  |

| JSSC-2007 [28]                                             | 0.18                       | 1.2-11.9    | 9.7      | 4.7     | -6.2          | 20                           | CG + noise cancellation                           |

| JSSC-2007 [29]                                             | 0.18 SiGe                  | 0.1-11      | 8        | 2.9     | -3.55         | 21.6                         | Distributed cascode + BW enhancement              |

| ISSCC-2007 [30]                                            | 0.13                       | 1-7         | 17       | 2.4     | -4.1          | 25                           | Cascode + CD FB                                   |

| JSSC-2008 [31]                                             | 0.13                       | 0.8-2       | 14.5     | 2.6     | 16            | 17.4                         | CG + noise and distortion cancellation            |

| MJ-2008 [32]                                               | 0.18                       | 5-6         | 20.5     | 1.8-2.6 | -6.2          | 2                            | Cascode + inter stage LC network                  |

| ISSCC-2009 [33]                                            | 0.18                       | 0.3-0.92    | 21       | 2       | -3.2          | 3.6                          | Differential CG + C Cross coupling                |

| ISSCC-2009 [34]                                            | 0.13                       | 3.1-10.6    | 15       | <4.5    | -12.5         | 26                           | Weighted distributed cascode                      |

| TCAS-II -2010 [35]                                         | 0.18                       | 3.1-10.6    | 13.9     | 4.7     | -8.5          | 14.4                         | Parallel RC FB                                    |

| MTT-s 2010 [36]                                            | 0.09                       | 3.1-10.6    | 10.5     | 3.2     | 4             | 21.6                         | Cs + Π input filter                               |

| MTT-S 2010 [37]                                            | 0.18                       | 3110.6      | 13       | 4.68    | -12           | 10.34                        | CS + RLC input filter                             |

| RFIC 2010 [38]                                             | 0.09                       | 21          | 15.4     | 6       | -6.6          | 12.5                         | Distributed CS + tapered transmission line        |

| MTT-2011 [39]                                              | 0.09                       | 0.01-1.77   | 23       | 2       | -2.85         | 2.8                          | Differential CG + multiple feedback               |

| IET MAP 2012 [40]                                          | 0.18                       | 2.4-11.2    | 14.8     | 3.9     | -11.5         | 3.4                          | CG + current reuse                                |

| MTT-2012 [41]                                              | 0.13                       | 0.6-3       | 42       | 3       | -14           | 30                           | Pseudo differential + resistive FB                |

| IJEC-2012 [42]                                             | 0.18                       | 3.1-10.6    | 15       | 3.5-3.9 | 6.4           | 16.2                         | Inverter with FB                                  |

| MWCL-2012 [43]                                             | 0.065                      | 0.01-2.8    | 32       | 1       | -13.6         | 40                           | Cascode + active -C element                       |

| TCAS-II-2013 [44]                                          | 0.18                       | 0-1.3       | 10       | 3       | +7.5          | 18                           | Cascode + active feedback                         |

| IJMST-2013 [45]                                            | 0.18                       | 2.5-16      | 11       | 3.3     | -             | 20                           | RC FB CS + current reuse                          |

| IJEC-2015 [46]                                             | 0.13                       | 2.35-9.37   | 10.3     | 3.68    | -4            | 9.97                         | CG current resue + noise cancelling               |

| MJ-2015[47]                                                | 0.13                       | 3.5-5       | 14       | 3.5-3.9 | 4             | 21                           | Fully differential + active FB + Noise cancelling |

TABLE I. LITERATURE SURVEY OF WIDEBAND LOW NOISE AMPLIFIER

### REFERENCES

- [1] Abidi, "The path to the software-defined radio receiver", IEEE J. Solid State Circuits 42 (5) (2007).

- [2] J. Mitiola,"The software radio architecture", IEEE Commun. Mag. 33 (5) (1995) 26–38

- [3] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nded., Cambridge University Press, Cambridge, U. K, 1998.

- [4] C. Toumazou, G. S. Moschytz, B. Gilbert, Trade-offs in Analog Circuit Design: The Designer's Companion, Part1, Springer, 2004.

## International Journal of Advance Research in Engineering, Science & Technology (IJAREST) Volume 3, Issue 1, January 2016, e-ISSN: 2393-9877, print-ISSN: 2394-2444

- [5] H. Hashemi, A. Hajimiri, "Concurrent multiband low-noise amplifiers theory, design and applications", IEEE Trans. Microwave Theory Tech. 50(1) (2002)288–301.

- [6] G. Sapone, G. Palmisano, "A 3–10GHz low-power CMOS low-noise amplifier for ultra-wideband communication", IEEE Trans. Microwave Theory Tech. 59 (3) (2011).

- [7] R. Roovers, D. M. W. Leenaerts, J. Bergervoet, K. S. Harish, R. C. H. Beek, G. Weide, etal., "An interference robust receiver for ultra-wideband radio in SiGe BiCMOS technology", IEEE J. Solid-State Circuits 40 (12) (2005) 2563–2572.

- [8] M. Brandolini, P. Rossi, D. Manstretta, F. Svelto, "Toward multi-standard mobile terminals—fully integrated receivers requirements and architectures", IEEE Tran. Microw. Theoryand Tech. 53 (3) (2005) 1026–1038.

- [9] R. Ludwig and P Bretchko, RF Circuit Design, 2000, Prentice Hall.

- [10] S. Andersson, C. Svenson, and O. Drugge, "Wideband LNA for a Multistandard Wireless Receiver in 0.18μm CMOS," Proceedings of the European Solid-State Circuits, September 2003, pp 655–658.

- [11] C.-W Kim, M.-S. Jung, S.-G. Lee, "Ultra-wideband CMOS low noise amplifier", Electronics Letters, vol. 41,no. 7,31 March 2005,pp. 384 385

- [12] S. Vishwakarma, J. Sungyong; J. Youngjoong; "Ultra Wideband CMOS Low Noise Amplifier With Active Input Matching", International Workshop on Ultra Wideband Systems, 2004. Joint with Conference on Ultra wideband Systems and Technologies. Joint UWBST & IWUWBS, 18-21 May 2004, pp. 415 – 419.

- [13] A. Bevilacqua, A. Niknejad, "An Ultra-Wideband CMOS LNA for 3.1 to 10.6 GHz Wireless Receivers", Digest of Technical papers of International Solid-State Circuits Conference, February 2004, pp. 382-383.

- [14] F. Bruccoleri, E.A.M. Klumperink, B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling", IEEE Journal of Solid-State Circuits, vol. 39, no. 2, Feb. 2004 pp. 275 282.

- [15] F. Bruccoleri, E.A.M. Klumperink, B. Nauta, "Noise cancelling in wideband CMOS LNAs", Digest of Technical Papers. ISSCC. 2002 IEEE International Solid-State Circuits Conference,vol.1, 3-7 Feb. 2002, pp. 406 407.

- [16] D. M. Pozar, Microwave Engineering, 2nd Edition, 1998, John Willey & Sons.

- [17] H.-T. Ahn, D.J. Allstot, "0.5-8.5 GHz fully differential CMOS distributed amplifier", IEEE Journal of Solid-State Circuits, vol. 37, no. 8, Aug. 2002, pp. 985 993.

- [18] B.M. Ballweber, R. Gupta and D.J. Allstot, "A Fully Integrated 0.5 5.5 GHz CMOS Distributed Amplifier", IEEE Journal of Solid-State, vol. 35, Feb. 2000, pp. 231-239.

- [19] R.-C. Liu, K.-L. Deng and H. Wang, "A 0.6-22GHz Broadband CMOS Distributed Amplifier", Dig. of Technical papers in RFIC Symp., 2003, pp. 103-106.

- [20] F.Bruccoleri, E. A. M. Klumperink, B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling", IEEE J. Solid-State Circuits39 (2) (2004).

- [21] A. Bevilacqua, A. Niknejad, "An ultra-wideband CMOS LNA for 3.1 to 10.6GHz wireless receivers", IEEE J.Solid-State Circuits 39 (12) (2004) 2259–2268

- [22] C. W. Kim, M. S. Kang, P. T. Anh, H. T. Kim, S. G. Lee, "An ultra wideband CMOS low noise amplifier for 3–5-GHz UWB system", IEEE J. Solid-State Circuits 40 (2) (2005)544–547.

- [23] M. S. Jung, C. W. Kim, P. T. Anh, H. T. Kim, S. G. Lee, "A 2.7–9.3 GHz CMOS wideband amplifier combined with high pass filter for UWB system", in Proceedings of 7<sup>th</sup> International Conference on Advanced Communication Technology (ICACT2005), February, 2005.

- [24] H. L. Kao, K. C. Chang, "Very low power CMOS LNA for UWB wireless receivers using current reused topology", J. Solid State Electron. no. 52 (2008) 86-90.

- [25] H.-Jin Lee, D. S. Ha, Sang S. Choi, "A 3–5 GHz CMOS UWB LNA with input matching using miller effect", IEEE International Solid-State Circuits Conference, 2006.

- [26] F. Zhang, P. R. Kinget, "Low power programmable gain CMOS distributed LNA", IEEE J. Solid-State Circuits 41 (6) (2006).

- [27] M. T. Reiha, J. R. Long, "A 1.2V reactive feedback 3.1-10.6GHz low-noise amplifier in 0.13 μm CMOS", IEEE J. Solid State Circuits 42 (5) (2007) 1023–1033.

- [28] C. Liao, S. Liu, "A broadband noise-canceling CMOS LNA for 3.1-10.6-GHz UWB receivers", IEEE J. Solid State Circuits 42 (2) (2007).

- [29] P. Heydari, "Design and analysis of a performance optimized CMOS UWB distributed LNA", IEEE J. Solid State Circuits 42 (9) (2007).

- [30] R. Ramzan, S. Andersson, J. Dabrowskiand C. Svensson, "A 1.4V 25mW inductorless wideband LNA in 0.13 um CMOS", IEEE international Solid-State Circuits Conference, pp.424–425.

- [31] W. Chen, G. Liu, B. Zdravko, A. Niknejad, "A highly linear broadband CMOS LNA Employing Noise and Distortion Cancellation", IEEE J. Solid-State Circuits 43 (5) (2008).

- [32] S. Toofan, A. R. Rahmati, A. Abrishamifar, G. Roientan Lahiji, "Low power and high gain current reuse LNA with modified input matching and inter-stage inductors", Microelectron. J. 39 (no.12) (2008) 1534–1537.

- [33] S. Woo, W. Kim, C. Lee, K. Lim, J. Laskar, "A 3.6mW Differential common gate CMOS LNA with positive negative feedback", IEEE International Solid-State Circuits Conference, 2009, pp.218–220.

- [34] Y. J. Wangand A. Hajimiri, "A compact low-noise weighted distributed amplifier in CMOS", in Proceedings of the IEEE International Solid State Circuits Conference, 2009, pp.220–222.

- [35] K. C. He, M. T. Li, C. M Li, J. H. Tarng, "Parallel RC feedback low noise amplifier for UWB applications", IEEE Trans. Circuits and Sys.—II: Express Briefs 57(8) (2010).

- [36] H. K. Chen, Y. S. Lin, S. S. Lu, "Analysis and design of a 1.6–28-GHz compact wideband LNA in 90-nm CMOS using a π-match input network", IEEE Trans. Microwave Theory Tech. 58 (8) (2010).

- [37] Y. Sheng Lin, C. Zhi Chen, H. Yu Yang, C. Chen, J. H. Lee, G. W. Huang, S. S. Lu, "Analysis and design of a CMOS UWB LNA with dual RLC branch wideband input matching network", IEEE Trans. Microwave Theory Tech. 58 (2) (2010).

- [38] B. Machiels, P. Reynaert, M. Steyaert, "Power efficient distributed low noise amplifier in 90nm CMOS", in Proceedings of the IEEE Proceedings of Radio Frequency Integrated Circuits Symposium, 2010, pp. 131–134.

- [39] E Ahmed Sobhy, Ahmed A Helmy, S Hoyos, K Entesari and E Sanchez-Sinencio, "A 2.8mW Sub 2dB Noise Figure Inductorless Wideband CMOS LNA Employing Multiple Feedback", in IEEE Trans. Of Microwave Theory and Techniques, Vol. 59 No. 12 December 2011 pp 3154-3161.

## International Journal of Advance Research in Engineering, Science & Technology (IJAREST) Volume 3, Issue 1, January 2016, e-ISSN: 2393-9877, print-ISSN: 2394-2444

- [40] J. Y. lee, H. K. Park, H. J. Chang and T. Y. Yun, "Low Power UWB LNA with common gate and current reuse techniques", IET Microw, Antennas Propag., 2012, vol. 6, Iss. 7, pp. 793-799.

- [41] X., Wang, J. Sturm, N. yan, X. Tan, and H. Min, "0.6-3GHz Wideband Receiver RF Front-End With a Feedforward Noise and Distortion Cancellation Resistive-Feedback LNA", IEEE Trans. On Microwave Theory and Techniques, vol. 60 no. 2 February 2012 pp. 387-392.

- [42] A. I. A. Galal, R. Pokharel, H. Kanaya and K. Yoshida, "High Linearity technique for ultra wideband low noise amplifier in 0.18um CMOS technology", International Journal of Electronics and Communication (AEU), Elsevier, 66 (2012) 12-17.

- [43] L. Belostotski, A. Madanayake and L. T. Bruton, "Wideband LNA with an Active –C Element", IEEE Microwave and Wireless Components Letters, vol. 22, no.. 10, October 2012 pp. 524-526.

- [44] Donggu Im, "A +9dBm output P1dB Active Feedback CMOS Wideband LA for SAW Less Receivers", IEEE Transaction on Circuits and Systems-II Express briefs, vol. 60, no. 7, july 2013, pp. 377-381.

- [45] K. Yousef, H. Jia, R. Pokharel, A. Allam, M. Ragab, H. Kanaya and k. Yoshida, "CMOS Ultra-Wideband Low Noise Amplifier Design", International Journal of Microwave Science and Technology, volume 2013.

- [46] S. Arshad, R. Ramzan, K. Khurram Muhammad and Q. ul Wahab, "A sub-10mW, noise cancelling, wideband LNA for UWB applications", International Journal of Electronics and Communications (AEU) Elsevier, (69) (2015) pp. 109-118.

- [47] A. Zoaei, and A. amirabadi, "A 130nm wideband fully differential linear low noise amplifier", Elsevier Microelectronics Journal, (46) (2015), 825-833.

- [48] Reza Molavi, "On the Design of Eideband CMOS Low Noise Amplifiers", Master Thesis of The University of British Columbia, September 2005

- [49] S. Arshad, F. Zafar, R. Ramzan and Q. Wahab, "Wideband and multiband CMOS LNA As: State of the art and future prospects", Elsevier Microelectronics Journal, April 2013.